Controlled Impedance PCB Design: Theory & Implementation

As digital signals push into the gigahertz range, traditional PCB traces can no longer be treated as simple conductors. When rise times are fast (e.g., <1 ns), the connection itself becomes a component. If that component (the trace) is not designed precisely, it will destroy signal integrity.

This is where Controlled Impedance is required.

This guide will walk you through the journey from understanding why signals distort, to calculating the necessary geometry, and finally, implementing those calculations in a complex PCB layout. Our goal is to ensure perfect signal integrity for high-speed protocols like DDR, PCIe, and USB-C.

Phase 1: Identifying the Problem (Reflections)

Why does a standard trace fail at high speeds? The problem is unexpected impedance changes. In basic circuit design, we assume wires have zero resistance and constant behavior. But a real PCB trace possesses finite distributed inductance (L) and capacitance (C).

If the impedance of the trace doesn't match the source (the driver IC) and the load (the receiver IC), the high-speed energy cannot be absorbed efficiently. It hits the mismatch and reflects back down the line. The result is visual chaos.

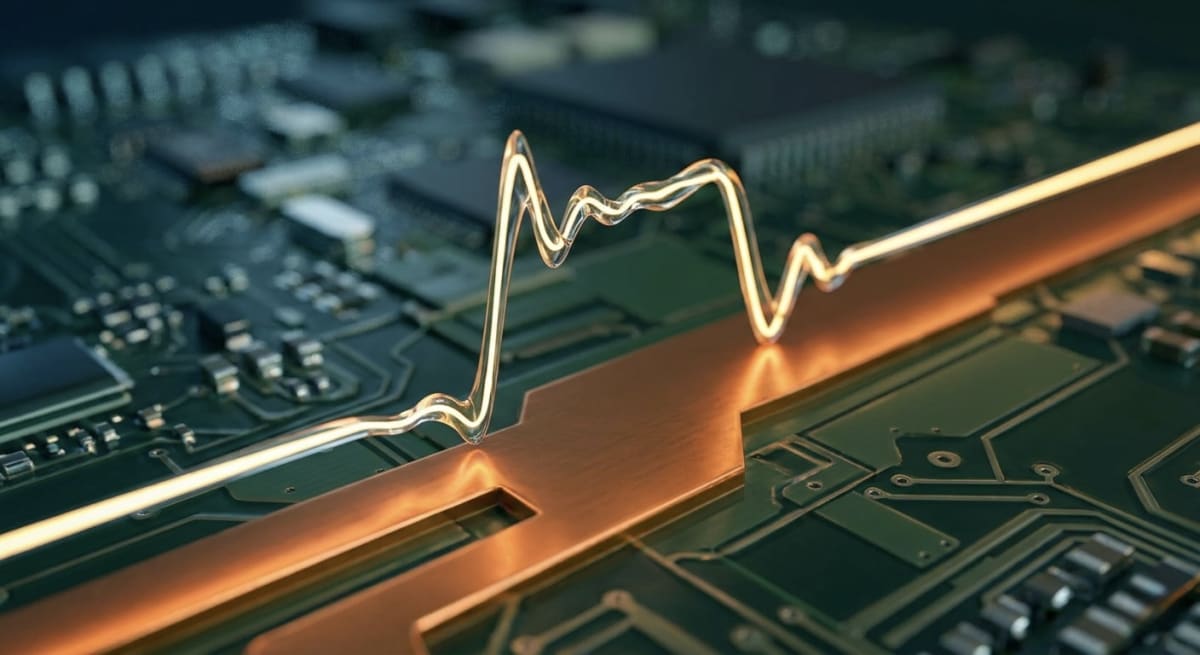

This close-up of a signal traveling down a simple copper trace shows reflections. As the signal tries to propagate, it hits impedance mismatches. It can no longer travel cleanly. This is the Signal Integrity (SI) problem that controlled impedance must solve. We see ringing and distortion, not a perfect square wave.

Phase 2: Transmission Line Theory (The Ideal Solution)

To fix the reflection problem seen in Image 1, we must treat the trace as a Transmission Line. We move from the physical chaos to an idealized theoretical model.

In this model, we understand that a high-speed signal doesn't flow through the trace, but between the trace and its reference (ground or power plane). The trace and the plane form an electromagnetic waveguide. We define the Characteristic Impedance (Z0) of that line, which must be perfectly uniform along its length to prevent the reflections seen in Image 1.

How is Z0 defined? In high-speed design, resistance (R) and conductance (G) are often negligible. We model the trace as a repetitive, distributed LC network of infinitesimal inductors and capacitors.

Our goal is not to eliminate L and C (which is impossible) but to control their distributed values precisely. We do this by defining the physical structure of the trace.

This idealized diagram visualizes a clean, theoretical solution that contrasts with the distortion shown in image_0.png. It models the trace as a series of distributed L and C components embedded in the dielectric. The trace runs smoothly above a ground plane, creating a precise, uniform characteristic impedance ($Z_0$). The signal wavefront is pristine as it travels (unlike the messy waveform from image_0.png), defining the ideal propagation.

Phase 3: Physical Geometry (The Implementation)

How do we actually define the distributed L and C shown in Image 2? We choose a physical structure. The prompt specifically requested we contrast Microstrip versus Stripline.

The primary difference between Microstrip and Stripline is where the trace is located relative to the dielectric and its ground planes.

Microstrip: The trace is on an outer layer (surface) and references a single ground plane beneath it.

Stripline: The trace is embedded within the core or prepreg, sandwiched symmetrically between two reference planes (both ground).

Stripline is the dominant choice for internal layers because the two ground planes provide excellent shielding and tighter containment of the electric fields, but it is often harder to manufacture and route.

We now define the parameters that will be used for calculations. These are:

W: Trace Width

H: Dielectric Height (H1, H2)

T: Trace Thickness (copper weight)

E_r: Dielectric Constant of the material (e.g., FR4, is \sim4.3)

This technical cross-section is a diagram comparing the two physical structures. On the left (Microstrip), the trace is on the surface and references one plane. On the right (Stripline), the trace is embedded between two planes. Notice how the electric fields are much more tightly contained and symmetrical in Stripline, which changes the L and C parameters (from Image 2). These dimensions are critical inputs for our calculation phase.

Phase 4: Essential Calculations (The Tool Solver)

Now that we have chosen a geometry (Microstrip or Stripline, defined in Image 3) and a specific material ($\text{Er}=4.3$), how do we calculate the trace width (W) and dielectric height (H) required to meet our target impedance (Z0) – typically 50 ohms for single-ended or 100 ohms for differential pairs?

For many decades, simple empirical formulas (like the ' IPC-2141A' or the original Wheeler formulas) were used. But they fail above 1 GHz due to high-frequency dielectric loss and skin effect.

Modern PCB design requires professional-grade field solver calculations. We no longer manually calculate, but derive the geometry (W, H, Er) using sophisticated boundary element method (BEM) algorithms.

We input the parameters into a software tool, and it generates the precise dimensions required.

This close-up of a high-speed PCB field solver screen shows the interface of a sophisticated calculator (like Polar Si9000). The user input fields for the parameters (W, H, Er from Image 3) are prominent. It captures the exact moment the designer enters 'Microstrip', '50 Ohms', 'Er=4.3', and 'W = 8.2 mils', then highlights the result, showing $Z_0 \approx 50.2$ Ohms, demonstrating that our design can meet the required impedance for the signal from image_0.png.

Phase 5: Practical Layout Implementation (The Stackup)

We have the theoretical model (Image 2), the chosen geometry (Image 3), and the calculated trace width and height (Image 4). How do we implement this during manufacturing?

The most critical step in implementing the calculations from Image 4 is defining the Layer Stackup. We define exactly how the board is constructed.

This image moves from theory (Image 1) to manufacturing. We must precisely control the dielectric thickness (H, measured below the trace in Image 3) and the material (Er). This means choosing a precise core and prepreg material (e.g., Rogers or Isola) and a precise copper weight.

We can visualize this with a macro photograph showing a real stackup of a multilayer board.

This precise, detailed macro photograph shows a manufactured 6-layer FR4 board stackup. It applies the calculation defined in Image 3 and 4. The digital caliper is precisely measuring the thickness between Layer 3 (a stripline trace defined by Image 2) and Layer 2 (Ground Plane). The caliper jaws focus our attention on the specific prepreg thickness ($H$ from Image 3). On the right, a graphical overlay displays the full stackup diagram (similar to the material composition implied in Image 1), detailing the layer order and materials: Core, Prepreg, copper weights, and target thicknesses derived from image_3.png. The focus is critical on the measured layer, showing precision manufacturing.

Phase 6: Expert Design Support and Layout (Best Practices)

The final step is to put everything together: the problem (Image 1), the theory (Image 2), the geometry (Image 3), the calculation (Image 4), and the manufacturing implementation (Image 5).

We must ensure Layout Best Practices are strictly followed during routing. The designer must maintain the continuous reference plane that defines the Z_0 structure.

This final image will show the implementation of the rules on a complex design, with expert support and Design Rule Check (DRC) validation. We zoom into a section of high-density differential pairs (DDR4 or PCIe) navigating a dense field.

The key to success is keeping the structure defined in Images 2 and 3 constant. We must avoid any discontinuities. We look for:

Perfectly uniform differential pair spacing.

Precise trace width (W from Image 3).

Crucially: ensuring there are no splits or voids in the continuous reference plane beneath these high-speed lines. A split reference plane immediately breaks the uniform structure from Image 2 and causes reflections (like those shown in Image 1).

This complex, high-speed top-down view of a professional PCB layout (e.g., DDR4 memory interface) shows expert design support. We zoom into a section of differential pairs highlighted in blue, which are referenced to the theoretical model shown in Image 2. A green DRC checkmark overlay shows 'Impedance Pass'. Crucially, a translucent green 'Keepout' zone graphic highlights a area on the continuous reference plane beneath these traces, explicitly avoiding a split reference plane. The lighting is screen glow, and it emphasizes that expert layout implementation is required to fulfill the manufactured stackup precision derived in image_4.png and image_5.png.

FAQ

What happens if I ignore controlled impedance in a high-speed design?

If impedance isn't strictly controlled, high-speed signals will reflect off impedance mismatches along the trace. This causes ringing, signal distortion, and timing errors, ultimately leading to data corruption, excessive EMI (Electromagnetic Interference), and complete circuit failure.

Is Stripline always better than Microstrip?

Not necessarily; they serve different purposes. Stripline offers superior electromagnetic shielding because the trace is sandwiched between two ground planes, making it ideal for routing sensitive high-speed signals on internal layers. Microstrip, located on the surface layers, is easier and cheaper to manufacture and has slightly faster signal propagation speeds. Your choice depends on your routing density and layer stackup.

Can I use standard math formulas to calculate my trace width?

For modern high-speed designs operating in the gigahertz range, traditional empirical formulas (like the older IPC equations) are no longer accurate enough due to high-frequency dielectric losses and the skin effect. It is highly recommended to use professional field solver software to determine the exact trace geometry required for your specific board materials.

What information must I provide to my PCB manufacturer to ensure my impedance targets are met?

You cannot just send the Gerber files; you must provide a detailed fabrication drawing. This drawing needs to include your exact layer stackup, specified dielectric materials (e.g., specific FR4 or Rogers core/prepreg), layer thicknesses, copper weights, and an impedance table. The table must list the target impedance (e.g., 50Ω single-ended or 100Ω differential), the calculated trace width/spacing, and which layers act as the reference planes.

Need help with your PCB design?

Our IPC CID+ certified team delivers production-ready designs with a 48-hour quote turnaround.